| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| 30 |

- 파이썬

- 컴공

- SSE

- 웹개발

- 백준풀이

- 코딩테스트

- ChatGPT

- 백엔드

- 코딩

- 모바일앱프로그래밍

- 컴퓨터공학

- 단위테스트

- 리액트

- 프로그래밍

- 프론트앤드

- spring

- 컴공생

- 이항계수

- 그리디

- 웹개발기록

- 알고리즘

- 그리디알고리즘

- 자료구조

- 백준1436

- 개발자

- boj11653

- 우선순위큐

- 백준

- 스프링

- 리액트네이티브

- Today

- Total

💻💭🎧🌏

Chapter 4. The Processor 본문

벌써 중간고사도 끝난 지 이주일이 지났지만.. 지금이라도 복습하는 습관을 길러보려고 시작합니다.

챕터 4에서 배울 내용

- 프로세스를 구현할 때 사용하는 규칙과 기술들

> Simplified design

> Piplelined design

- Core instructions들의 부분집합의 구현

> 메모리 참조(Memory-reference) : ld, sd

> 산술 논리(arithmetic-logic) : add, sub, and, or

> 조건 브랜치(conditional branch) : beq

- Instruction set 구조가 어떻게 많은 구현의 측면을 결정하는지

- 다양한 구현 전략들이 clock rate 와 CPI에 어떻게 영향을 미치는지

Overview of Implementation

명령어 실행하는 초기 두 단계가 있다.

1. 수행할 명령어를 PC 레지스터에서 가져온다.

2. 레지스터를 읽는다

> ld는 1개의 레지스터를 읽는다.

> 다른 대부분의 명령어는 2개의 레지스터를 읽는다.

- 각 단계들은 명령어 클래스(memor-reference, arthmetic-logical, or branches) 에 의존한다.

- RISC-V의 단순성과 규칙성은 명령어들이 유사하게 실행되도록 만든다.

-> 최대한 같은 부분이 커지도록 / isntruction들을 최대한 유사하게

ex) ALU 가 사용되는 곳

- 산술적인 결과를 도출할 때 (add, sub, ...)

- 메모리 주소 (ld)

- 브랜치가 갈 곳의 주소 (beq)

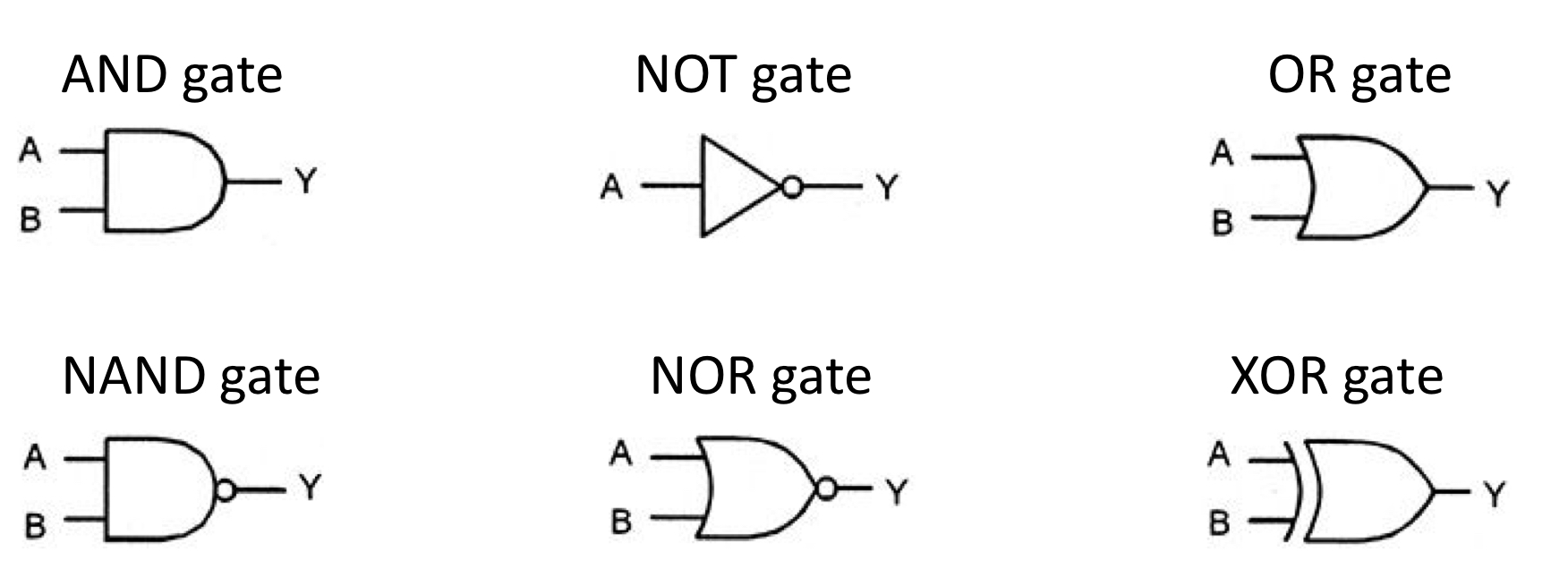

Logic Design Basics

논리회로 수업을 들으면서 배운 간단한 내용이므로 설명 생략

Digital Logic Element types

두 가지 요소가 있다.

1. Combinational element

- 입력이 즉각 반영된다.

- 데이터 상에서 실행한다.

- 내부 저장공간이 없다. (메모리 역할을 하는 기능이 없다.)

- Output은 Input의 함수이다.

-> 같은 Input이라면 항상 같은 Output이 나온다는 의미이다.

2. State (Sequential) element

- 상태들이 내부 저장공간에 저장된다.

- 최소 2개의 input과 1개의 output이 있어야 한다.

-> input : data value, clock

- Output은 현재의 input 뿐만 아니라 이전의 Input 값에도 영향을 받는다.

- 입력이 들어와도 Clock Signal에 의해 통제가 가능하다.

- 입력은 하나지만 출력은 여러 개일 수도 있다. -> 같은 Input이라도 다른 Output이 나올 수 있다는 의미인 것 같은데 확실하지 않아서 다시 확인해봐야 할 것 같다.

Clocks : 읽고 쓰는 시간은 제어되어야 한다.

- 읽기와 쓰기의 시간이 같으면 ouput은 예측 불가능하다.

Edge-triggered clocking

- 아래에서 위로 올라가거나 위에서 아래로 내려가는 등의 변화되는 시점을 Edge 라고 한다.

- Sequential logic element에서의 데이터는 clock edge 에서만 업데이트된다.